- Turnkey Solution

-

가온칩스는 시제품 Test부터 양산 생산/공급까지 빠른 TAT를 달성하기 위하여

세계 최고의 Foundry, PKG, Test 기업과 긴밀한 파트너십을 구축하고 있습니다.

장기적이고 전략적인 파트너십 프로그램으로 업계 최고 grade의 공정 및 PKG / Test 기술의

성공적인 case study를 쌓음으로써 고객에게 PKG / Test / Q.A / Mass Production

전체 Process에 걸쳐 Total Solution을 제공합니다.

-

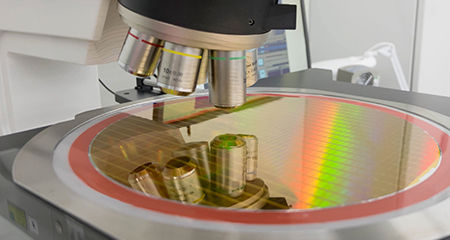

- Wafer Business

- Wafer fabrication without Wafer probing

-

- Known Good Die Business

- Wafer fabrication including Wafer probing

-

- Turnkey Business

- Complete all fabrication (Foundry / Package / Test)

-

01

Package Design Solution

-

Package Bump/Substrate Design

High-End Design (2.5D/3D PKG, Interposer Design) for AI/HPC Products

High-Reliability Packaging Solutions for Automotive Applications

-

02

Package Validity Check

-

Thermal Simulation/Thermal Solution Service

Electrical (RLC, IR Drop, S-Parameter) Simulation

Mechanical Simulation

-

03

Package Assembly Solution

-

Assembly Process & Condition Setup

Parameter Optimization (DOE)

Clean BOM Composition

-

01

Signal Integrity

-

Signal Integrity by Channel/Transient Simulation

Signal Margin Assessment by EYE Diagram

Providing Solutions: Off-Chip Design (PKG+Board) Optimization

-

02

Power Integrity

-

Power Integrity by PDN (Power Distribution Network) Analysis

Power Noise Check & Decap (Decoupling Capacitance) Optimization

Providing Solutions: Decap Budgeting to Reduce Power Noise

-

01

Support for Test Solution

-

IP Test Vector Generation to ATE Test Setup

Corner Characteristics Analysis for Mass Production Evaluation

Test Program Development

-

02

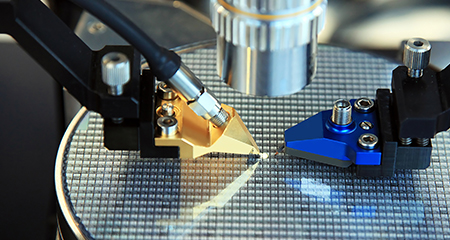

Test Material

-

Load Board/Probe Card Design

Load Board/Probe Card Manufacturing (Outsourcing)

IC Test Socket

Test Material Maintenance

-

03

Test Setup

-

Test Setup Interface with Test House

Test Vector Debugging Support

-

04

Mass Production Support

-

Low Yield Analysis

Product Characterization

Test Time Optimization

-

01

Yield Enhancement

-

Continuous Yield Trend Monitoring & Analysis

Yield Stabilization

Corner Test, Process Sweet Spot Identification

-

02

Mass-Production Control

-

Customer Forecast Management

Outsourcing Capacity Control (FAB, Package, Test)

Invoice, Build Instruction, WIP Monitor

Wafer/Package/Test Yield Control

Risk Management

-

03

Raw Material Inventory Control

-

Wafer, Package Substrate, EMC, Packing Material

-

04

Delivery Control

-

TAT, Shipping, Logistic Management

-

01

Customer Quality Service

-

Approval Documentation (PPAP etc.)

Customer Quality Issue Handling

Automotive Service Pack Solution

Customer Audit Support

-

02

Product Qualification

-

Reliability Test based on AEC-Q100 or JEDEC

Manufacture Process Qualification

Supplier Certification/Regular Audit

-

02

Quality Management

-

Quality Management System by ISO Compliance

Outsourcing Quality Control

Nonconforming Lot Handling & Monitoring

Failure Analysis for Customer Return & Reliability Failure